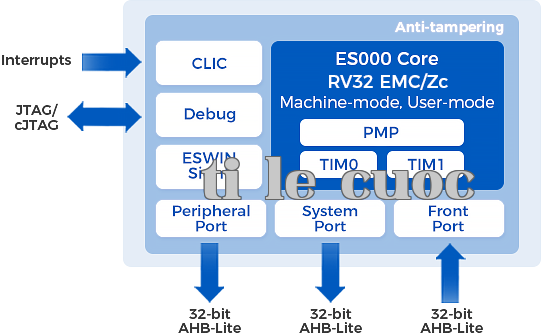

Nó thực hiện hơn mười chức năng an toàn chống giả mạo đối với nhiều mô hình tấn công;

Hỗ trợ tính năng ESWIN Sight, cung cấp công cụ phân tích sóng (waveform debugging), giúp người dùng dễ dàng theo dõi trạng thái bên trong và các sự kiện diễn ra trong CPU một cách trực quan và hiệu quả.

| Đặc điểm | Mô tả | ||||

| Kiến trúc tập lệnh | RISC-V 32 bit EMC/Zc_Zicsr_Zifencei | ||||

| Chế độ | Chế độ máy (Machine-mode) và chế độ người dùng (User-mode) | ||||

| An ninh |

Hỗ trợ Smepmp, có thể chọn 0-16 khu vực bảo vệ bộ nhớ vật lý (PMP Region)

Hỗ trợ hơn mười chức năng an toàn như phân cực ngẫu nhiên đường truyền dữ liệu, đồng bộ chu kỳ lệnh, v. sicbo |

||||

| Đường ống | 2 cấp_PIPELINE | ||||

| Bộ nhớ trong của bộ xử lý | TIM0 và TIM1, kích thước có thể cài đặt (0KB-128MB), ECC có thể chọn | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ 112 yêu cầu ngắt, hỗ trợ ngắt không thể bỏ qua (NMI) | ||||

| Gỡ lỗi | Module gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG | ||||

| Giao diện tổng thể |

1. Giao diện ngoại vi (Peripheral Port): Giao diện chủ AHB 32 bit;

2. Giao diện hệ thống (System Port): Giao diện chủ AHB 32 bit (có thể tùy chọn); Cổng đầu vào (Front Port): Giao diện AHB 32 bit, được sử dụng để truy cập từ bên ngoài vào TIM0 và TIM1, hỗ trợ kết nối linh hoạt và hiệu suất cao trong các hệ thống điều khiển. sicbo |

||||

| CoreMark(CoreMarks/MHz) | 2.15 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 0.87 | ||||

Số đăng ký mạng Quảng Đông 11030102011303

Số đăng ký mạng Quảng Đông 11030102011303