Bộ vi xử lý này hỗ trợ đầy đủ tập lệnh RISC-V DSP phiên bản V0.9.11, bao gồm các phần mở rộng Zpn, Zbpbo và Zpsfoperand, tổng cộng có 244 lệnh đặc biệt giúp tối ưu hóa khả năng xử lý tín hiệu số trong các ứng dụng công nghiệp và truyền thông tại khu vực miền Trung.

Hỗ trợ RISC-V N-Trace.

| Đặc điểm | Mô tả | ||||

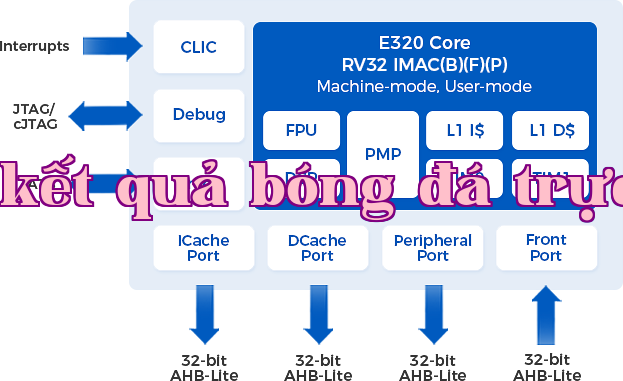

| Kiến trúc tập lệnh | E320 tuân thủ tiêu chuẩn RISC-V 32 bit với bộ mở rộng IMAC(B)(F)(P)_Zicsr_Zifencei_Zicbom, cung cấp khả năng tính toán mạnh mẽ và linh hoạt cho các ứng dụng yêu cầu cao như điều khiển tự động và xử lý tín hiệu thời gian thực tại TP. Trang cá cược | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ người dùng (User-mode) | ||||

| An ninh | Hỗ trợ Smepmp, có thể chọn 0-16 khu vực bảo vệ bộ nhớ vật lý (PMP Region) | ||||

| Đường ống | Bộ xử lý có 3 cấp độ luồng | ||||

| Bộ nhớ trong của bộ xử lý | TIM0 và TIM1, kích thước đều có thể cấu hình (0KB-128MB) | ||||

| Bộ đệm lệnh L1 (L1 I$) | Kích thước có thể cấu hình (4KB-128KB) | ||||

| Bộ đệm dữ liệu L1 (L1 D$) | Kích thước có thể cấu hình (4KB-128KB) | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ lên đến 496 yêu cầu ngắt, hỗ trợ ngắt không thể bỏ qua (NMI) lich ngoai hang anh | ||||

| Ghi lại và theo dõi lỗi |

Module gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG

Modul theo dõi (Trace module) hỗ trợ RISC-V N-Trace |

||||

| Giao diện tổng thể |

1. Giao diện bộ nhớ đệm lệnh (ICache Port): Giao diện chủ AHB-Lite 32 bit

2. Giao diện bộ nhớ đệm dữ liệu (Dcache Port): Giao diện chủ AHB-Lite 32 bit 3. Giao diện thiết bị ngoại vi (Peripheral Port): Giao diện chủ AHB-Lite 32 bit 4. Giao diện phía trước (Front Port): Giao diện từ AHB-Lite 32 bit |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.74 | ||||

Số đăng ký mạng Quảng Đông 11030102011303

Số đăng ký mạng Quảng Đông 11030102011303