Dựa trên kiến trúc E320, nhà sản xuất đã tích hợp thêm các module như Parity/ECC và SPM (Stack Pointer Monitor), nhằm đảm bảo hệ thống đạt được cấp độ an toàn chức năng ASIL-B, phù hợp với các tiêu chuẩn nghiêm ngặt trong ngành công nghiệp ô tô. keo ca cuoc

| Đặc điểm | Mô tả | ||||

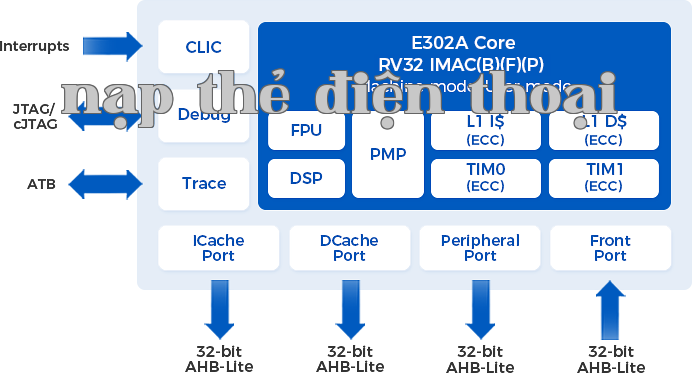

| Kiến trúc tập lệnh | RISC-V 32 bit với bộ chỉ thị IMAC(B)(F)(P)_Zicsr_Zifencei_Zicbom, mang đến sự linh hoạt và mở rộng cao cho các ứng dụng nhúng, đặc biệt là trong môi trường yêu cầu an toàn cao như xe tự lái hay hệ thống điều khiển thân xe tại thành phố Đà Nẵng. | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ người dùng (User-mode) | ||||

| An ninh | Hỗ trợ Smepmp, có thể chọn 0-16 khu vực bảo vệ bộ nhớ vật lý (PMP Region) | ||||

| Đường ống | Bộ xử lý có 3 cấp độ luồng | ||||

| Bộ nhớ trong của bộ xử lý | TIM0 và TIM1, kích thước có thể cài đặt (0KB-128MB), ECC tùy chọn | ||||

| Bộ đệm lệnh L1 (L1 I$) | Kích thước có thể cấu hình (4KB-128KB), có thể chọn Parity/ECC | ||||

| Bộ đệm dữ liệu L1 (L1 D$) | Kích thước có thể cấu hình (4KB-128KB), có thể chọn Parity/ECC | ||||

| Ngắt | Bộ điều khiển ngắt CLIC, hỗ trợ lên đến 496 yêu cầu ngắt, hỗ trợ ngắt không thể bỏ qua (NMI) sicbo | ||||

| Ghi lại và theo dõi lỗi |

Module gỡ lỗi (Debug module) hỗ trợ JTAG/cJTAG

Modul theo dõi (Trace module) hỗ trợ RISC-V N-Trace |

||||

| Giao diện tổng thể |

1. Giao diện bộ nhớ đệm lệnh (ICache Port): Giao diện chủ AHB-Lite 32 bit

2. Giao diện bộ nhớ đệm dữ liệu (Dcache Port): Giao diện chủ AHB-Lite 32 bit 3. Giao diện thiết bị ngoại vi (Peripheral Port): Giao diện chủ AHB-Lite 32 bit 4. Giao diện phía trước (Front Port): Giao diện từ AHB-Lite 32 bit |

||||

| CoreMark(CoreMarks/MHz) | 4.45 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 1.74 | ||||

Số đăng ký mạng Quảng Đông 11030102011303

Số đăng ký mạng Quảng Đông 11030102011303