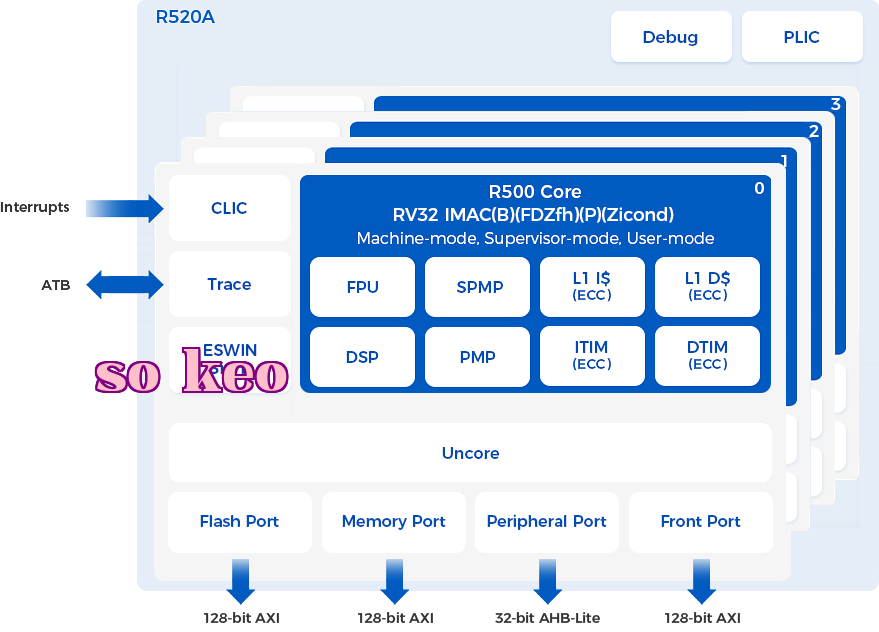

Hỗ trợ tập lệnh RV32GCBP, cùng nhiều mở rộng chính thức như Zfh (nửa độ chính xác), Zicbom (thao tác bộ nhớ đệm), Zicond (chạy điều kiện), Zicsr (đọc/ghi CSR), Zifence (rào cản lấy lệnh), SmePMP (bảo vệ địa chỉ nâng cao), SPMP (bảo vệ địa chỉ chế độ giám sát), SBA (truy cập hệ thống bus) và nhiều tính năng khác, đảm bảo khả năng linh hoạt và hiệu quả trong nhiều môi trường ứng dụng. ti le cuoc

Cung cấp các chức năng tiên tiến như PPMA (kiểm tra thuộc tính bộ nhớ chương trình có thể lập trình), đồng bộ bộ nhớ đệm, Stack Monitor (giám sát ngăn xếp), ESWIN Sight (phân tích tín hiệu nội bộ), N-Trace (theo dõi luồng lệnh), giúp tối ưu hóa hiệu suất và độ tin cậy của hệ thống. keo ca cuoc

Hỗ trợ chế độ Dual-Core LockStep (hai lõi đồng bộ), với hai chế độ hoạt động: Split và Lock. Trong chế độ Lock, hai lõi R500A hoạt động đồng bộ, cho phép phát hiện lỗi trong quá trình chạy hệ thống và báo cáo thông qua môi trường tích hợp. Trong chế độ Split, các lõi có thể tách biệt, thực thi các chuỗi lệnh độc lập, từ đó nâng cao hiệu năng và thích nghi tốt hơn với nhiều ứng dụng khác nhau.

Hỗ trợ nhiều cơ chế an toàn chức năng: bảo vệ giao diện bus, bảo vệ giao diện SRAM và tách biệt các mô đun không an toàn;

Phù hợp với nhiều hệ điều hành thời gian thực như RTOS, μClinux và cả Linux hỗ trợ SPMP, mang lại sự linh hoạt cao trong việc lựa chọn nền tảng phần mềm cho các thiết kế phức tạp.

Được thiết kế để đáp ứng nhu cầu xử lý ngắt nhanh chóng, sản phẩm này rất phù hợp cho các thiết bị công nghiệp, thiết bị y tế, thiết bị lưu trữ, Modem, 5G, truyền tải video trực tiếp và đặc biệt thích hợp cho các hệ thống ECU/DCU trên xe và thiết kế IC ô tô. Trang cá cược

| Đặc điểm | Mô tả | ||||

| Kiến trúc tập lệnh |

RV32

IMAC(B)(FDZfh)(P)_Zicsr_Zifencei_Zicbom_(Zicond) _Zilsd |

||||

| Đường ống | Đường dẫn phát hành siêu quy mô 6 cấp, phát hành song song theo thứ tự, có bộ dự đoán nhánh (Branch Predictor) | ||||

| Chế độ | Chế độ máy (Machine-mode), chế độ giám sát (Supervisor-mode), chế độ người dùng (User-mode) | ||||

| An ninh |

Vùng bảo vệ PMP có thể lên đến 16 vùng, vùng bảo vệ SPMP có thể lên đến 16 vùng;

Hỗ trợ kiểm tra PPMA (thuộc tính bộ nhớ vật lý có thể lập trình) |

||||

| Bộ nhớ tích hợp lệnh (ITIM) | Kích thước 0-2MB có thể tùy chỉnh, ECC có thể chọn | ||||

| Bộ nhớ tích hợp dữ liệu (DTIM) | Kích thước 0-2MB có thể tùy chỉnh, ECC có thể chọn | ||||

| Bộ đệm chỉ thị L1 (L1 I$) | Kích thước bộ nhớ đệm có thể tùy chỉnh từ 0KB đến 128KB, cấu hình 2 cách nhóm, đường dẫn 64B, hỗ trợ ECC tùy chọn | ||||

| Bộ đệm dữ liệu L1 (L1 D$) | Kích thước bộ nhớ đệm có thể tùy chỉnh từ 0KB đến 128KB, cấu hình 4 cách nhóm, đường dẫn 64B, hỗ trợ ECC tùy chọn | ||||

| Đơn vị tính toán số thập phân (FPU) | Hỗ trợ độ chính xác kép, độ chính xác đơn, và mở rộng số thập phân bán độ chính xác RISC-V Zfh | ||||

| Đơn vị xử lý tín hiệu số (DSP) | Hỗ trợ mở rộng RISC-V RV32P đầy đủ | ||||

| Ngắt |

Hỗ trợ bộ điều khiển ngắt CLIC, mỗi lõi hỗ trợ tối đa 1008 ngắt nhanh

Hỗ trợ bộ điều khiển ngắt PLIC, hỗ trợ tối đa 1024 nguồn ngắt bên ngoài Hỗ trợ ngắt không thể bỏ qua NMI có thể phục hồi |

||||

| Ghi lại và theo dõi lỗi |

Modul gỡ lỗi (Debug module) hỗ trợ giao tiếp JTAG/cJTAG và cổng truy cập hệ thống bus (SBA)

Modul theo dõi (Trace module) hỗ trợ RISC-V N-Trace |

||||

| Giao diện tổng thể |

1. Giao diện Flash (Flash Port): giao diện chủ AXI chỉ đọc 128 bit

2. Giao diện bộ nhớ (Memory Port): giao diện chủ AXI 128 bit 3. Giao diện ngoại vi (Peripheral Port): giao diện chủ AXI 32 bit Cổng trước (Front Port): Giao diện AXI 128 bit, sử dụng để truy cập bên ngoài vào ITIM, DTIM và DCache |

||||

| CoreMark(CoreMarks/MHz) | 5.79 | ||||

| Dhrystone-Legla(DMIPS/MHz) | 2.55 | ||||

Số đăng ký mạng Quảng Đông 11030102011303

Số đăng ký mạng Quảng Đông 11030102011303